# (12) United States Patent

### Crooks

#### (54) SPECTRUM ANALYZER USING MULTIPLE INTERMEDIATE FREQUENCIES AND MULTIPLE CLOCK CONFIGURATIONS FOR RESIDUAL, SPURIOUS AND IMAGE SIGNAL REDUCTION

(75) Inventor: **Justin Crooks**, La Center, WA (US)

Assignee: Test Equipment Plus, Inc, La Center,

WA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 633 days.

(21) Appl. No.: 13/026,876

(22)Filed: Feb. 14, 2011

(65)**Prior Publication Data**

> US 2011/0202316 A1 Aug. 18, 2011

#### Related U.S. Application Data

- (60) Provisional application No. 61/304,291, filed on Feb. 12, 2010.

- (51) **Int. Cl.** G01R 19/02 (2006.01)G06G 7/20 (2006.01)G01R 19/03 (2006.01)G01R 23/16 (2006.01)

- (52) U.S. Cl. CPC ...... *G01R 23/16* (2013.01) USPC ........... 702/198; 455/323; 455/324; 455/326; 455/338; 327/113; 327/116; 327/119

- Field of Classification Search USPC ........ 702/198; 324/76.19-76.32, 41, 69, 85, 324/310, 680

See application file for complete search history.

## (45) Date of Patent:

## US 8,977,519 B2 Mar. 10, 2015

#### (56)References Cited

(10) Patent No.:

#### U.S. PATENT DOCUMENTS

| 3,675,136 A * 3,740,748 A *   |        | O'Brien                  |

|-------------------------------|--------|--------------------------|

| 6,108,529 A *                 | 8/2000 | Vice et al 455/323       |

| 6,111,911 A *                 |        | Sanderford et al 375/147 |

| 6,307,868 B1 * 6,654,595 B1 * |        | Rakib et al              |

| 6,684,065 B2*                 |        | Bult et al               |

| 6,834,187 B1*                 |        | Weber et al              |

| 7,212,050 B2 *                | 5/2007 | Meltzer 327/156          |

| 7,317,765 B2*                 | 1/2008 | Jones et al 375/305      |

#### (Continued)

#### OTHER PUBLICATIONS

Hunter, et. al., "Fundamentals of Modern Spectral Analysis", IEEE AUTOTESTCON 2010 in Orlando, FL, US, Sep. 14, 2010, pp. 1-21. (Continued)

Primary Examiner — Tung S Lau Assistant Examiner — Stephanie Chang (74) Attorney, Agent, or Firm — Rylander & Associates, PC; Philip R. M. Hunt

#### (57)ABSTRACT

A spectrum analyzer for measuring an RF signal over a selected frequency span configured to use multiple Intermediate Frequencies (IFs) for residual, spurious and image signal reduction. The spectrum analyzer has both a primary IF path and a secondary IF path configured to provide band pass filtering of the IF signals. A master clock synthesizer is configured to reduce residual noise by providing from a single Voltage Controlled Oscillator, a master clock signal and a Local Oscillator (LO) signal. The spectrum analyzer has a microcontroller configured to change the frequency of the master clock signal and the LO signal if the center frequency of the selected span is sufficiently close to a known spurious signal.

#### 11 Claims, 4 Drawing Sheets

# US 8,977,519 B2 Page 2

| (56)                             | 20000      | ces Cited            | 2011/0202316 A1*        | 8/2011      | Arthaber                           |

|----------------------------------|------------|----------------------|-------------------------|-------------|------------------------------------|

| U.S. PATENT DOCUMENTS            |            |                      | 2011/0320148 A1*        | 12/2011     | Hillman, Jr 702/77                 |

| 2001/0041548 A                   |            | Bult et al 455/252.1 | 2012/0263393 A1*        | 10/2012     | Yahil                              |

| 2002/0047942 A                   |            |                      | OTHER PUBLICATIONS      |             |                                    |

| 2002/0050861 A<br>2005/0002449 A |            | Nguyen et al         |                         |             |                                    |

| 2005/0002449 A<br>2005/0003785 A |            | Jackson et al        | Barrett, "Fractional/In | teger-N PI  | L Basics", Texas Instruments, Dal- |

| 2005/0003703 A                   |            | Weste et al          | las, TX, US, Apr. 22, 2 | 2010, pp. 1 | -55.                               |

| 2006/0046678 A                   |            | Noda et al 455/285   | Stewart, Spectrum An    | alysis Bas  | ics Application Note 150, Agilent, |

| 2006/0120730 A                   | 1* 6/2006  | Drentea 398/201      | US, Aug. 2, 2006, pp.   | 1-120.      |                                    |

| 2006/0229046 A                   | 1* 10/2006 | Bult et al 455/252.1 |                         |             |                                    |

| 2007/0091814 A                   | 4/2007     | Leung et al 370/252  | * cited by examiner     |             |                                    |

FIG.2

FIG.4

#### SPECTRUM ANALYZER USING MULTIPLE INTERMEDIATE FREQUENCIES AND MULTIPLE CLOCK CONFIGURATIONS FOR RESIDUAL, SPURIOUS AND IMAGE SIGNAL REDUCTION

#### CROSS-REFERENCE TO RELATED APPLICATION

This application claims priority to U.S. Provisional Patent 10 Application Ser. No. 61/304,291 filed Feb. 12, 2010, incorporated herein by reference.

#### FIELD OF THE INVENTION

The present invention relates generally to electronic test equipment, and more particularly, to radio frequency (RF) spectrum analyzers and measuring receivers.

#### BACKGROUND

The term "spectrum analyzer" refers to a device used to examine the spectral composition of a radio frequency (RF) input signal. A typical spectrum analyzer will allow a user to select a frequency span defined by a span center frequency 25 and a span width. The typical spectrum analyzer will then divide the frequency span into segments ("bins") and for each frequency bin in the span, measure input signal energy associated with frequencies in the bin. The result is typically shown on a visual display as a graph with the frequencies of 30 the span on the horizontal axis and the input signal energy per bin on the vertical axis. The RF input signal may comprise one or more component signals at different frequencies, each displayed as a peak on the vertical axis.

A digital spectrum analyzer typically consists of several 35 sections, including an RF section, a local oscillator (LO) section, an intermediate frequency (IF) section, a digital processing section and a display. The RF section typically includes an attenuator to reduce the RF input signal amplitude, one or more stages of mixers to convert the RF input 40 signal to an intermediate frequency (IF) signal using local oscillator signals from one or more local oscillators (LO) in the LO section. The IF signal has several components. A desired component is a frequency shifted version of the input RF. The IF signal will also have undesired components, 45 including residual, spurious and image signals. The IF section typically has a system of filtering the IF signal to eliminate out-of-band signals, including IF signal components that are frequency shifted replicas of RF signal components that were not in the selected span and including some of the unwanted 50 residual, spurious and image signals. The IF section also typically has an analog to digital converter for converting the analog IF signal to a set of digitized IF signal samples. The digital processing section typically has hardware or software rier Transforms (FFT) of the time domain set of digitized IF signal samples to a frequency domain set of digitized IF signal samples and for making various measurements of the digital time and frequency domain sets of the IF signal samples.

Spectrum analyzers generate undesired residual, spurious and image signals. Residual signals are false signals that are displayed with no input into the spectrum analyzer, and are typically generated from the electronic circuitry of the spectrum analyzer itself. Spurious signals ("spurs") are false sig- 65 nal products that result when an input signal is applied. Image signals are the undesired one of a summed frequency signal

2

and a difference frequency signal, both of which are generated when mixing the RF input signal with an LO signal.

To minimize the introduction of unwanted residual signals. a spectrum analyzer typically isolates the LO, RF, IF and digital processing sections using shielding, which adds considerable weight and cost. Spectrum analyzers often use a Yttrium Iron Garnet (YIG) LO, which requires several watts of power and is expensive, but provides a clean signal which adds minimal phase noise to the input signal.

Measuring receivers are used to measure precise relative signal amplitude measurements over a wide dynamic range, measure peak and average modulation characteristics and apply filters to the IF analog and digital signals. Frequency modulation and amplitude modulation characteristics may be measured. Precise amplitude steps may be measured as well. Measuring receivers are typically separate devices from spectrum analyzers, in spite of sharing many functional blocks.

Many modern spectrum analyzers use the Fast Fourier Transform (FFT) technique to convert time-domain signal 20 data into frequency-domain signal data. Processing highresolution FFTs quickly requires a powerful processor.

Handheld spectrum analyzers contain less expensive, less accurate components, have less shielding and consume less power than a traditional rack-mount spectrum analyzer. They typically have a low resolution display and buttons for a user interface. They are generally not capable of processing automated commands and are of minimal usefulness in a lab setting. They generally have slower processors which are not capable of quickly processing very large FFTs. With less accurate components, less powerful processors and less shielding, handheld spectrum analyzers do a poor job of reducing residual, spurious and image signals and have poorer overall results than a larger, high quality spectrum

RF cables are often used to connect spectrum analyzers to a signal being measured and can be a major source of measurement inaccuracies. RF cables typically have unknown, frequency-dependent losses which change as the cable is bent or twisted. It is often not very convenient to place a large spectrum analyzer near the source of an RF signal or orient it in such a way to minimize bending of the RF cables.

Owning a modern spectrum analyzer with good specifications is currently cost prohibitive for many students, inventors, and amateur radio enthusiasts.

What is needed is an ultra-low-cost, low-power, lightweight, portable spectrum analyzer similar in size and weight to a traditional RF power sensor; a spectrum analyzer that can be connected close to the source of a signal being measured without long intervening RF probe cables yet carries the signal processing power of the modern personal computer.

#### SUMMARY AND ADVANTAGES

An embodiment of a spectrum analyzer is disclosed herein for performing additional filtering, for performing Fast Fou- 55 for measuring an RF signal over a selected frequency span, the spectrum analyzer configured to use multiple Local Oscillator (LO) signals to generate multiple Intermediate Frequencies (IFs) for residual, spurious and image signal reduction. The disclosed spectrum analyzer has both a primary IF path and a secondary IF path, each configured to provide band pass filtering of the multiple IF signals. A master clock synthesizer is configured to reduce residual noise by providing a master clock signal and a second stage Local Oscillator (LO) signal, both from a single Voltage Controlled Oscillator (VCO). The spectrum analyzer has a microcontroller configured to change the frequency of the master clock signal and the second stage LO signal if the center frequency of the selected span is

sufficiently close to a known spurious signal using the current second stage LO signal. The disclosed spectrum analyzer performs spectrum analysis on DC-coupled RF signals from 1 Hz to 4.4 GHz. The disclosed spectrum analyzer embodiment is USB bus-powered.

A method is disclosed for the selection of variable LO, clock, and IF frequencies to effectively mask out image, spurious and residual signals across several ranges of input frequencies. A method is disclosed for reducing the effects of internally generated residual signals. A method is disclosed for providing rapid frequency sweeps of large spans without the use of a sweep oscillator.

Additional advantages of the invention will be set forth in part in the description which follows, and in part will be obvious from the description, or may be learned by practice of the invention. The advantages of the invention may be realized and attained by means of the instrumentalities and combinations particularly pointed out in the appended claims. Further benefits and advantages of the embodiments of the invention will become apparent from consideration of the following detailed description given with reference to the accompanying drawings, which specify and show preferred embodiments of the present invention.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are incorporated into and constitute a part of this specification, illustrate one or more embodiments of the present invention and, together with the detailed description, serve to explain the principles <sup>30</sup> and implementations of the invention.

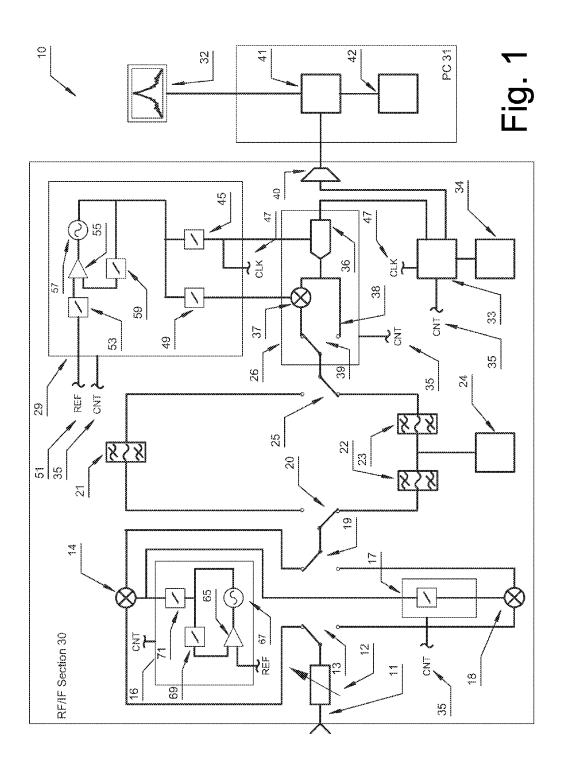

FIG. 1 is a block diagram of the spectrum analyzer in accordance with an exemplary embodiment of the present invention.

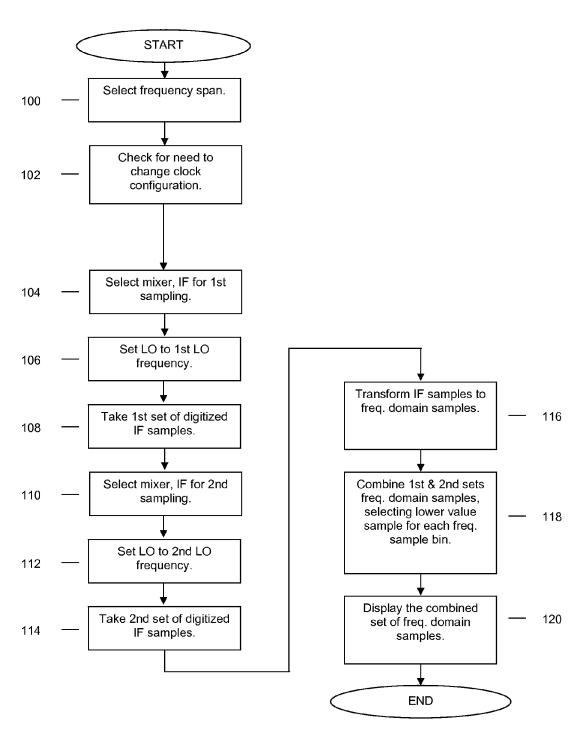

FIG. 2 shows a flow chart of a method used by the spectrum <sup>35</sup> analyzer of FIG. 1 for measuring the RF signal.

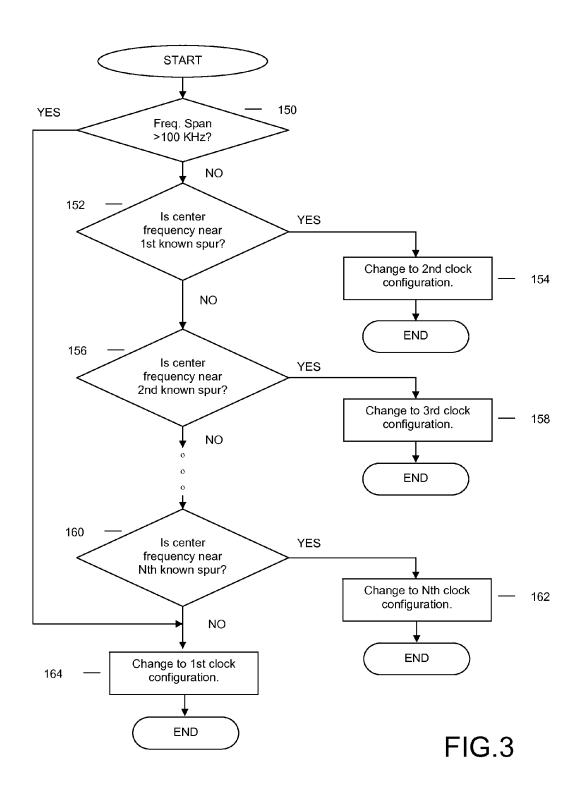

FIG. 3 shows a flow chart of a method for a spectrum analyzer to change clocking configuration to eliminate spurious signals when measuring an RF signal over a selected frequency span with a center frequency.

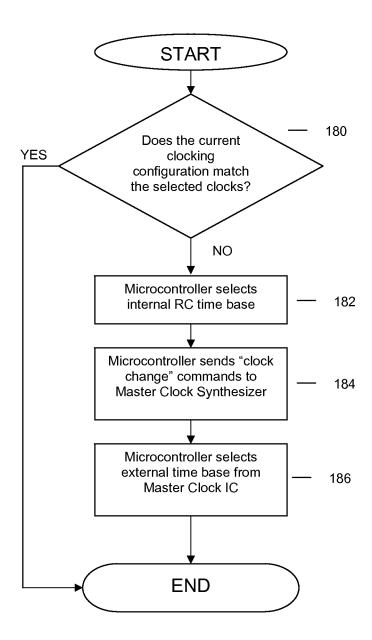

FIG. 4 shows a flow chart of a method for changing clock configuration.

#### REFERENCE NUMBERS USED IN DRAWINGS

Turning now descriptively to the drawings, in which similar reference characters denote similar elements throughout the several views, the figures illustrate the spectrum analyzer of the present invention. With regard to the reference numerals used, the following numbering is used throughout the 50 various drawing figures:

| Reference<br>Numbers | Part References                          |  |  |

|----------------------|------------------------------------------|--|--|

| 10                   | spectrum analyzer                        |  |  |

| 11                   | RF input                                 |  |  |

| 12                   | input attenuator                         |  |  |

| 13                   | first RF path switch                     |  |  |

| 14                   | high band mixer                          |  |  |

| 16                   | wideband synthesizer                     |  |  |

| 17                   | low band divider                         |  |  |

| 18                   | low band mixer                           |  |  |

| 19                   | second RF path switch                    |  |  |

| 20                   | first IF path switch                     |  |  |

| 21                   | secondary IF filter                      |  |  |

| 22                   | primary IF impedance<br>matching network |  |  |

4

-continued

|    | Reference<br>Numbers | Part References          |

|----|----------------------|--------------------------|

| 5  | 23                   | primary IF filter        |

|    | 24                   | wideband RMS power       |

|    |                      | detector                 |

|    | 25                   | second IF path switch    |

|    | 26                   | IF-to-Bits circuit IC    |

|    | 29                   | master clock synthesizer |

| 10 | 30                   | RF/IF section            |

|    | 31                   | personal computer PC     |

|    | 32                   | display                  |

|    | 33                   | microcontroller          |

|    | 34                   | memory                   |

|    | 35                   | control line             |

| 15 | 36                   | Analog to Digital        |

|    |                      | Convertor ADC            |

|    | 37                   | second stage mixer       |

|    | 38                   | mixer bypass             |

|    | 39                   | mixer bypass switch      |

|    | 40                   | data port                |

| 20 | 41                   | processor                |

|    | 42                   | pc memory                |

|    | 45                   | clock divider            |

|    | 47                   | clock line               |

|    | 49                   | second stage LO divider  |

|    | 51                   | reference signal input   |

| 25 | 53                   | reference divider        |

|    | 55                   | master phase             |

|    | 57                   | comparator               |

|    | 57                   | master VCO               |

|    | 59                   | master VCO divider       |

|    | 61                   | LO reference signal      |

| 30 | 65                   | input                    |

| 50 | 65<br>65             | LO phase comparator      |

|    |                      | LO VCO                   |

|    | 67<br>69             | LO VCO LO VCO counter    |

|    |                      |                          |

|    | 71                   | high band divider        |

#### DETAILED DESCRIPTION

Before beginning a detailed description of the subject invention, mention of the following is in order. When appropriate, like reference materials and characters are used to designate identical, corresponding, or similar components in differing figure drawings. The figure drawings associated with this disclosure typically are not drawn with dimensional accuracy to scale, i.e., such drawings have been drafted with a focus on clarity of viewing and understanding rather than dimensional accuracy.

In the interest of clarity, not all of the routine features of the implementations described herein are shown and described. It will, of course, be appreciated that in the development of any such actual implementation, numerous implementation-specific decisions must be made in order to achieve the developer's specific goals, such as compliance with application- and business-related constraints, and that these specific goals will vary from one implementation to another and from one developer to another. Moreover, it will be appreciated that such a development effort might be complex and time-consuming, but would nevertheless be a routine undertaking of engineering for those of ordinary skill in the art having the benefit of this disclosure.

FIG. 1 shows an embodiment of a spectrum analyzer 10 configured to generate multiple Intermediate Frequencies (IF) for residual, spurious and image signal reduction. The spectrum analyzer 10 is configured to examine the spectral composition of a radio frequency (RF) input signal. The spectrum analyzer 10 is configured to allow a user to select a frequency span by selecting a span center frequency and a

span width. The spectrum analyzer 10 is configured to divide the frequency span into segments ("bins") and for each frequency bin in the span, measure input signal energy associated with frequencies in the bin. The spectrum analyzer 10 is comprised of an integrated RF/IF section 30, a personal computer (PC) 31 configured for digital signal processing and a display 32. The RF/IF section 30 is configured to convert the RF signal to a first set of digitized IF signal samples using a first Local Oscillator (LO) signal that has a first LO frequency and to convert the RF signal to a second set of digitized IF signal samples using a second Local Oscillator (LO) signal that has a second LO frequency. The PC 31 is configured to convert the first and second set of digitized IF signal samples to first and second sets of frequency domain samples. The PC 31 is further configured to combine the first and second set of frequency domain samples into a combined set of frequency domain samples by selecting, for each frequency sample bin, the lower valued frequency domain sample of the first and second IF frequency domain samples associated with that 20 frequency sample bin. The display 32 is configured to visually present the combined frequency domain samples.

The RF/IF section 30 has master clock synthesizer 29 configured to provide clocking to the various components of the RF/IF section using methods that reduce or eliminate 25 unwanted residual and spurious signals. The RF/IF section 30 includes an RF/IF microcontroller 33 configured to execute various procedures to control and coordinate the actions of the various RF/IF section 30 components over control lines 35 and an RF/IF memory 34 configured to store the instructions for the various control procedures.

An RF portion of the RF/IF section 30 includes an RF input 11, an input attenuator 12, a first RF path switch 13, a high band mixer 14, a low band mixer 18, a second RF path switch 19, a wideband synthesizer 16, and a low band divider 17. A 35 high band RF path is defined as a signal path from the first RF path switch 13 through the high band mixer 14 to the second RF path switch 19. A low band RF path is defined as a signal path from the first RF path switch 13 through the low band mixer 18 to the second RF path switch 19. An RF signal 40 applied to the RF input 11 is routed to the input attenuator, which in the exemplary embodiment is a CMOS digital step attenuator. The attenuated RF signal is then routed to the first RF path switch 13, selecting the high band RF path leading to the high band mixer 14 or the low band RF path leading to the 45 low band mixer 18. A high band local oscillator (LO) signal for the high band mixer 14 is generated by the wideband synthesizer 16. A low band LO signal for the low band mixer 18 comes from the low band divider 17 which is driven by the high band LO signal generated by the wideband synthesizer 50 16. When the first and second RF path switches are selected for the high band RF path, the attenuated RF signal is mixed with the high band LO signal in the high band mixer 14 to produce an IF signal. When the first and second RF path switches are selected for the low band RF path, the attenuated 55 RF signal is mixed with the low band LO signal in the low band mixer 18 to produce an IF signal. All IF signals generated by either the high band mixer 14 or the low band mixer 18 are considered first stage IF signals. Two different RF paths are provided because a practical RF mixer will not perform 60 well at both high and low frequencies. The low band mixer 18 is selected to have good performance at low frequencies and the high band mixer 14 is selected to have good performance at high frequencies. In the exemplary embodiment, the low band mixer 18 is a Mini-Circuits ADE-1ASK and the high 65 band mixer is a Mini-Circuits ADE-42MH. In the exemplary embodiment, the low band RF path is used for RF signals with

6

frequencies equal to or less than 150 MHz and the high band RF path is used for RF signals with frequencies greater than 150 MHz.

The RF/IF section 30 is configured to generate each LO signal with a frequency selected such that when the LO signal is mixed with the RF signal, the IF signal generated is the RF signal frequency shifted to a primary IF or a secondary IF. That is, the IF signal will have energy at the primary IF in proportion to energy at the center span frequency in the RF signal and, each IF frequency will have energy in the same proportion to energy in an RF frequency where the difference between the IF frequency and the primary IF is the same as the difference between the RF frequency and the center span frequency of the RF signal. In the exemplary embodiment, the primary IF is 10.7 MHz and the secondary IF is 2.9 MHz.

The RF/IF section 30 is configured to sequentially convert the RF signal to a first IF signal using a first LO signal with a first LO frequency, then convert the RF signal to a second IF signal using a second LO signal with a second LO frequency. In some instances, both first and second IF signals are generated sequentially by the high band mixer 14, one after the other. In other instances one of the IF signals is generated by the high band mixer 14 while the other IF signal is generated by the low band mixer 18. In yet other instances, both first and second IF signals are generated sequentially by the low band mixer 18, one after the other.

The low band mixer 18, is placed in the low band RF signal path with IF and RF ports reversed, allowing frequencies down to DC to be up-converted, or higher frequencies to be down-converted, without changing hardware configuration.

The RF/IF section 30 includes an IF filtering portion with a first IF path switch 20, a secondary IF filter 21, a primary IF impedance matching network 22, a primary IF filter 23, a wideband RMS power detector 24 and a second IF path switch 25. A primary IF path is defined as a signal path from the first IF path switch 20 through the primary IF filter 23 to the second IF path switch 25. A secondary IF path is defined as a signal path from the first IF path switch 20 through the secondary IF filter 21 to the second IF path switch 25. The secondary IF filter 21 has center frequency selected to match the secondary IF. The primary IF impedance matching network 22 and primary IF filter 23 have center frequencies selected to match the primary IF. In the exemplary embodiment, the secondary IF filter 21 has a center frequency of 2.9 MHz and the primary IF impedance matching network 22 and primary IF filter 23 have center frequencies of 10.7 MHz. The bandwidth of the secondary IF filter 21 and the primary IF filter 23 are selected to match the bandwidth of the ADC 36. The bandwidth of the primary IF impedance matching network 22 is selected to facilitate large span measurements using the RMS power detector 24, which will be described in greater detail below. In the exemplary embodiment, the secondary IF filter 21 and the primary IF filter 23 have bandwidths of 280 kHz. The bandwidth of the primary IF impedance matching network 22 is 5 MHz.

The RF/IF section 30 is configured to sequentially convert the RF signal to a first IF signal using a first LO signal with a first LO frequency, then convert the RF signal to a second IF signal using a second LO signal with a second LO frequency. In some instances, both first and second IF signals pass through the primary IF path, one after the other. In other instances one of the IF signals passes through the primary IF path while the other IF signal passes through the secondary IF path. In yet other instances, both first and second IF signals pass through the secondary IF path, one after the other.

The RF/IF section 30 includes a second stage IF mixing portion which includes a second stage mixer 37, a mixer

bypass 38, and a mixer bypass switch 39. The IF mixing portion is followed by an Analog to Digital Converter (ADC) **36**. If the second IF path switch **25** is set to shunt an IF signal from the primary IF path, then the mixer bypass switch 39 is configured to shunt the IF signal to the second stage mixer 37. 5 The second stage mixer 37 is configured to convert the first stage, primary IF signal into a second stage IF signal using a second stage LO signal with a second stage LO. The frequency of the second stage LO is selected to make center frequency of the second stage IF signal match the center frequency of the ADC 36. If the second IF path switch 25 is configured to shunt an IF signal from the secondary IF path, then the mixer bypass switch 39 is set to shunt the IF signal through the mixer bypass 38 and straight to the ADC 36. The ADC **36** is configured to convert either the second stage IF signal, or the secondary IF signal, depending on the state of the mixer bypass switch 39, into a set of digitized IF signal samples comprising interleaved in-phase and quadraturephase (I/Q) data samples. The ADC 36 sends the set of digitized IF signal samples as a serial digital signal, via micro- 20 controller 33 and a data port 40, out of the RF/IF section 30 to the PC 31. In the exemplary embodiment, the microcontroller 33 acts as a multiplexer to interleave the digitized IF signal samples with communications between the microcontroller 33 in the RF/IF section 30 and the processor 41 in the PC 31. 25 In the exemplary embodiment, the data port 40 conforms to one of the Universal Serial Bus standards.

In the exemplary embodiment, an "IF-to-bits" integrated circuit (IC) **26**, the Analog Devices AD9864, is used to provide the second stage mixer **37**, the mixer bypass **38**, the 30 mixer bypass switch **39** and the ADC **36**. In the AD9864, the center frequency of the ADC **36** is ½ of the frequency of the clock signal provided to the ADC **36**.

The RF/IF section 30 having two IF paths can produce some distinct advantages. In the exemplary embodiment, The 35 2.9 MHz secondary IF path yields a flat response and is 10 dB more sensitive than the 10.7 MHz primary IF path, but has much larger spurious signals from poorly filtered out-of-band signals. The 10.7 MHz primary IF path, with its additional filtering and mixing stage, is less sensitive but provides better 40 out-of-band spurious rejection. Measurements are further enhanced by setting one local oscillator signal to yield an IF signal with the 2.9 MHz secondary IF and using the 2.9 MHz secondary IF path while setting the second local oscillator signal to yield an IF signal with the 10.7 MHz primary IF and 45 using the 10.7 MHz primary IF path. The displayed average noise level benefits from the sensitivity of the 2.9 MHz secondary IF path while the spurious signals are by and large masked out by combining the digitized 2.9 MHz IF signal with the 10.7 MHz IF signal in the masking process.

The PC 31 has a processor 41 and a PC memory 42. The processor 41 is configured to execute digital signal processing (DSP) methods for processing the sets of digitized IF signal samples received from the RF/IF section 30. Such methods include performing FFTs on the first and second set of digitized IF signal samples to transform them into first and second sets of frequency domain samples; and combining first and second sets of frequency domain samples into a composite set of frequency domain samples, masking out unwanted images and spurious signals in the process. The PC memory 42 is configured to store the instructions for the DSP methods. The PC memory 42 may also be configure configured to store the combined frequency signals. The PC memory 42 may be volatile or non-volatile memory.

The RF/IF path switches (the first RF path switch 13, the 65 second RF path switch 19, the first IF path switch 20, the second IF path switch 25 and the mixer bypass switch 39) are

8

all controlled by the RF/IF microcontroller **33** through control lines **35**. In the exemplary embodiment, the RF/IF path switches are transistor switches capable of sub-millisecond switching.

The RF/IF section 30 has a master clock synthesizer 29 configured to generate the second stage LO signal and a master clock signal. The master clock synthesizer 29 comprises an internal integer-N Phase Lock Loop (PLL) that includes a reference signal input 51, a reference divider 53, a master phase comparator 55, a master Voltage Controlled Oscillator (VCO) 57, and a master VCO divider 59. The PLL is configured to convert a frequency reference signal to a master VCO signal. The master VCO 57 generates the master VCO signal at a frequency controlled by a voltage supplied by the master phase comparator 55. The reference divider 53 divides the frequency of the reference signal  $F_{ref}$  by a reference divisor M, resulting in a signal to the master phase comparator 55 with a frequency 1/M of the reference frequency. The master VCO divider 59 divides the frequency of the master VCO signal  $(F_{MVS})$  by a master VCO divisor  $N_{MV}$ , resulting in a signal to the phase comparator with a frequency  $1/N_{MV}$  of the master VCO signal frequency. As such, the PLL will lock the master VCO signal frequency  $\mathbf{F}_{MV\!S}$  equal to the reference signal  $F_{ref}$  times the reference divisor M divided by the master VCO divisor  $N_{MV}$ , as stated by the equation:  $F_{MVS} = F_{ref} \times M/N_{MV}$ .

The master clock synthesizer 29 has a second stage LO divider 49 configured to divide the master VCO signal by a second stage LO divisor integer  $N_{LO2}$  to produce the second stage LO signal at a second stage LO frequency  $F_{LO2}$  that is  $1/N_{LO2}$  of the master VCO signal frequency. The master clock synthesizer 29 has a second stage LO signal output configured to send the second stage LO signal to the second stage mixer 37

The master clock synthesizer 29 has a clock divider 45 configured to divide the master VCO signal by a clock divisor integer  $N_{CLK}$  to produce a master clock signal at a master clock signal frequency  $F_{CLK}$  that is  $1/N_{CLK}$  of the master VCO signal frequency. The master clock synthesizer 29 has clock outputs configured to send the master clock signal to the ADC 36 and also to the RF/IF microcontroller 33 via a clock line 47

Providing both the clocking to the ADC 36 and the LO signal to the second stage mixer 37 from the same VCO reduces the amount of noise introduced to the IF signals. Additionally, all the other components in the RF/IF section 30 that require clocking either receive the master clock signal directly from the master clock synthesizer 29 or from the RF/IF microcontroller 33, which may divide down the frequency for other components. Thus all major sources of clock noise are at substantially the same frequency or fractions thereof, which makes mitigating clock induced noise a simpler task.

The values of the master clock synthesizer **29** divisors (the reference divisor M, the master VCO divisor  $N_{MP}$ , the clock divisor integer  $N_{CLK}$ , and the second stage LO divisor integer  $N_{LO2}$ ) are closely interrelated and should be selected carefully. There are several considerations. In the exemplary embodiment, the master clock synthesizer **29** is a Texas Instruments CDCE906. Values must be found so that the master VCO **57** operates at frequencies in its allowable range, which for the CDCE906 is between 100 MHz and 200 MHz. Values must be found so that the resulting second stage IF signal after second stage LO mixing has a center frequency near to the center frequency of the ADC **36**, which for the AD9864 is one-eighth of the frequency of the clock supplied to the ADC **36**. Better control of phase noise is achieved

where  $N_{MV}$  is kept to a minimum and values selected that have been found not to produce overlapping spurious signals. In the exemplary embodiment, a reference signal with a frequency of 10 MHZ is used.

In the exemplary embodiment, three configurations of the 5 master clock synthesizer **29** are used, as shown in Table 1:

10

Fractional-N spur signals are injected into the IF signal by the wideband synthesizer **16** as a function of denominator C and post-scalar factor P. As discussed above, image and spur rejection is achieved by mixing the RF signal with two distinct LO signals at different frequencies to generate two IF signals, combining the frequency-domain samples of the two

TABLE 1

| Config. | M   | $N_{MV}$ | $N_{CLK}$ | $N_{LO2}$ | $F_{MVS}$ | $\mathbf{F}_{CLK}$    | $F_{LO2}$ |

|---------|-----|----------|-----------|-----------|-----------|-----------------------|-----------|

| 1       | 14  | 1        | 6         | 18        | 140 MHz   | 23½ MHz               | 7½ MHz    |

| 2       | 27  | 2        | 6         | 10        | 135 MHz   | 22½ MHz               | 13.5 MHz  |

| 3       | 327 | 2        | 7         | 21        | 163.5 MHz | 23% <sub>17</sub> MHz | 7.784 MHz |

The values in configurations 1-3 were selected for their non-overlapping residual and spurious signals as well as their low divisors. The third configuration is needed to avoid residual signals from the master clock signal frequencies in the first two configurations, at multiples of 630 MHz. The 20 third configuration has spurious signals at frequencies that are dissimilar to the other configurations.

If self-generated residual or spurious signals occur at the RF frequency being measured, the clock frequency is automatically changed to reduce interference. Changing clock 25 frequencies needs to occur quickly and seamlessly. To accomplish this, the RF/IF microcontroller 33 switches the clocking between measurements. The RF/IF microcontroller 33 first switches to an internal resistor-capacitor (RC) clock, then writes the new clock settings to the master clock synthesizer 39, and finally switches back to the master clock signal when it is stable at the new master clock frequency. This is transparent to the user.

The wideband synthesizer 16 comprises a fractional-N Phase Lock Loop (PLL) that includes an LO reference signal 35 input 61, an LO phase comparator 65, an LO Voltage Controlled Oscillator (VCO) 67, and an LOVCO counter 69. The PLL is configured to convert a frequency reference signal to an LO VCO signal. The LO VCO 67 generates the LO VCO signal at a frequency controlled by a voltage supplied by the 40 LO phase comparator 65. The reference signal  $F_{ref}$  is fed to the LO phase comparator 65. The LO VCO counter 69 alters the LO VCO signal frequency  $(F_{LVS})$  by a multiple of an LO counter factor  $(CF_{LO})$ , which is equal to the quantity of an integer A, plus a numerator B divided by denominator C, the 45 quantity divided by 2 to the power of a post-scalar factor P. As such, the PLL will lock the LO VCO signal frequency  $F_{LVS}$ equal to the reference signal  $F_{ref}$  times the LO counter factor (CF<sub>LO</sub>), as stated by the equation:  $F_{LVS} = F_{ref} \times (A+B/C)/2^P$ . In the exemplary embodiment, the wideband synthesizer 16 is 50 an Analog Devices ADF4350. For the ADF4350 integer A can have values of 220-440 inclusive. Numerator B is forced to be less than 900, typically much less. Denominator C can be equal to or greater than 2 and less than 900, must be a prime number, and is typically less than 100. The post-scalar factor 55 P can be 0-4 inclusive, or 4-10 inclusive when using the ADF4007 for the low band divider 17.

In the exemplary embodiment, reference signal  $F_{ref}$  at 10 MHz is converted to an LO VCO signal at an LO VCO frequency  $F_{LVS}$  between 2.2 GHz and 4.4 GHz, which is then 60 divided in a high band divider 71 by 1, 2, 4, 8, or 16 internally to produce the high band LO signal for the high band mixer 14. The high band LO signal is further divided externally by 8, 16, 32, or 64 in the low band divider 17 to produce the low band LO signal for the low band mixer 18. In the exemplary 65 embodiment, the low band divider 17 is an Analog Devices ADF4007.

IF signals, then for each frequency bin in the selected span, accepting only the lower valued frequency domain sample associated with that frequency sample bin, thereby masking out unwanted residual, spurious and image signals since each such unwanted signal occurs at a different frequency in each of the two IF signals. For most pairs of LO signals, values of the denominator C used to generate them will be such that the fractional-N spur signals do not occur at the same frequency and the spurs will be masked out. However, it is possible that values of denominator C can be selected such that some of the fractional-N spurs occur at the same frequency and will not be masked out. To ensure that fractional-N spurs from the LOs are masked out, values for the denominator C must be prime, but different, integers for the two selected frequencies. The two distinct values of C each must be the minimal values for which an LO frequency exists that is sufficiently close to the ideal LO frequency for the desired measurement. In the exemplary embodiment, an LO frequency within 5% of the center frequency of the span under test +5 kHz is considered sufficiently close.

Additionally, the ADC **36** has a residual signal which needs to be eliminated. Integer A, numerator B, denominator C and post-scalar P are selected such that the LO spurs and the ADC **36** residual signals are not overlapping. Thus any image, residual, and spurious signal do not line up at the same frequency in an IF signal generated at one LO frequency as they will in an IF signal generated at another LO frequency and are canceled during the masking process.

In the exemplary embodiment, twelve distinct combinations of clocks and mixing are available for each RF frequency span examined. The LO signal can be injected with a frequency on the high side of the RF signal or on the low side, the resulting IF can be 2.9 MHz or 10.7 MHz, and one of three clock configurations can be selected. This allows substantial flexibility when reducing image, spur and residual signals. This flexibility in system clocks also reduces the need for shielding since the spectrum analyzer 10 can automatically configure clocking to avoid self-generated noise. This reduces overall size and weight, allowing construction of a smaller, more portable device. Increased portability will in many cases eliminate the need for an RF cable between the RF/IF section 30 and the source of RF signal being measured, yielding a spectrum analyzer that can be connected like an RF power sensor and benefit from the increased accuracy from the lack of RF cables.

These features of the spectrum analyzer 10 allow RF and IF sections of the spectrum analyzer 10 to be integrated more closely and with less shielding than in previous designs, providing for a more compact and lower cost device. However, one of skill in the art will realize that the various innovative features described herein may be practiced without integrating the RF and IF sections and eliminating shielding.

For very low RF frequencies, near or below the operating frequency of the low band mixer 18 or the low band divider 17, image suppression cannot be achieved by mixing the RF signal with LO signals with frequencies on the high side and low side of the RF signal. Instead, two local oscillator signals 5 are used with LO signals with frequencies on the high side of the RF signal separated only by tens of kilohertz. The aforementioned masking technique is used to reject the image, since the image will shift the opposite direction than the desired signal.

11

To achieve full span sweeps of 4.25 GHz in just a few seconds, the ADC 36 cannot be utilized due to its narrow bandwidth. Therefore, a wideband RMS power detector 24 monitors the output of the primary IF impedance matching network 22. The bandwidth of ~5 MHz allows stepping of the 13 LO by 3 MHz across the selected span and taking a wide IF power level reading at each step. By assuming the RF input signal will at each step produce a high-side IF signal with peaks at frequencies that are a sum of the RF and LO frequencies and a low-side IF signal with peaks at frequencies that are 20 a difference of the RF and LO frequencies, the spectrum analyzer 10 can mask out any low-side IF signal peak that does not have a corresponding high-side IF signal peak, then take a series of more accurate power readings at frequencies near the low side IF signal peaks using the ADC 36. Thusly, a 25 analyzer to change clocking configuration to eliminate spufull span sweep can be achieved with full amplitude accuracy in a few seconds.

FIG. 2 shows a flow chart of a method used by the spectrum analyzer 10 of FIG. 1 for measuring the RF signal. Step 100 is selecting a frequency span. This step may be performed 30 manually by a user manipulating controls or by commands from an automated script. Step 102 is checking whether the clocking configuration needs to be changed. This is a check for known spurious signals generated by clocking within the spectrum analyzer that may be near to the center frequency of 35 the span. FIG. 3 discusses this step is greater detail.

Step 104 is selecting an intermediate frequency (IF) for the first sampling from one of a primary IF and secondary IF. To obtain a measurement of the selected frequency span, at least two samplings are performed. If the width of the span is larger 40 than the bandwidth of the ADC 36, then the span is divided into segments each equal to the width of the ADC 36 bandwidth and two samplings are performed for each segment. Step 104 also includes selecting a mixer for a first sampling. Either the high band mixer 14 or low band mixer 18 may be 45 selected. In the exemplary embodiment, the high band mixer 14 is selected in all cases except where the center frequency of the selected frequency span is less than 150 MHz. Once IF and mixer have been selected for the first sampling, the RF/IF path switches are set to create a first signal path through the 50 mixer for the first sampling and an IF path associated with the IF for the first sampling. Step 106 is setting a first stage local oscillator (LO) signal to a first LO frequency. This is based on the selected span and the IF selected for the first sampling. The LO frequency must be such that its sum or difference with 55 the center frequency of the selected span equals the selected IF. Step 108 is taking a first set of digitized IF samples with the ADC 36.

Step 110 is selecting a mixer for the second sampling. Once again, either the high band mixer 14 or the low band mixer 18 60 may be selected, regardless of the selection for the first sampling. Step 110 also includes selecting an intermediate frequency (IF) for the second sampling. Once again, either the primary IF or the secondary IF may be selected, regardless of the selection that was made for the first sampling. Once IF and mixer have been selected for the second sampling, the RF/IF path switches are set to create a second signal path through the

12

mixer for the second sampling and an IF path associated with the IF for the second sampling. Step 112 is setting the first stage local oscillator (LO) to a second LO frequency. This is based on the selected span and IF for the second sampling. The LO frequency must be such that its sum or difference with the center frequency of the selected span equals the selected IF. Step 114 is taking a second set of digitized IF samples.

Step 116 is transforming the first and second sets of digitized IF samples to a first and a second set of frequency domain samples. This is done with an FFT. Step 118 is combining the first and second set of frequency domain samples into a combined set of frequency domain samples. The combining is done by looking at the samples associated with the same frequency sample bin in both sample sets and selecting whichever has a lower value frequency domain sample. The higher value frequency sample is discarded. In this way, unwanted signals are masked out, as they will only have peak values in one of the two sample sets.

Step 120 is displaying the combined set of frequency domain samples. In other embodiments, the combined set is stored. In yet other embodiments, the combined set is displayed and stored.

FIG. 3 shows a flow chart of a method for a spectrum rious signals when measuring an RF signal over a selected frequency span with a center frequency. Step 150 is checking the selected frequency span width and if the selected span is greater than 100 KHz wide then Step 164 is performed for changing to a first clock configuration (see Table 1 for clock configurations) and the method terminates. If the selected span is not greater than 100 KHz wide, then step 152 is performed.

Step 152 is checking if the center frequency of the selected span is near a first known spurious signal or integer multiples thereof and if so, Step 154 is performed for changing to a second clock configuration and the method terminates. In this method, the center frequency of the selected span is considered near a spurious signal if it is within half of the ADC 36 bandwidth. In the exemplary embodiment, half of the ADC 36 bandwidth is about 100 KHz. If the center frequency of the selected span is not near the first known spurious signal or integer multiples thereof, then step 156 is performed.

Step 156 is checking if the center frequency of the selected span is near a second known spurious signal or integer multiples thereof and if so, Step 158 is performed for changing to a third clock configuration and the method terminates. If the center frequency of the selected span is not near the second known spurious signal or integer multiples thereof, then step 160 is performed.

Step 160 is a repeat of steps 152 and 156 for an Nth known spurious signal or integer multiples thereof. In the exemplary embodiment, only two spurious signals are known: 630 MHz (and integer multiples thereof) and 23½ MHz (and integer multiples thereof).

FIG. 4 shows flow chart of a method for changing clock configuration. This method is performed after the method of FIG. 3 determines the clocking configuration to be used in a measurement. Step 180 is checking if the current clocking configuration matches that selected by the method of FIG. 3. If the current clocking configuration matches the selected clocking configuration, then this method terminates. If not, Step 182 is performed. Step 182 has the microcontroller 33 select an internal RC time base. Step 184 has the microcontroller 33 send a clock change command to the master clock synthesizer 29. Step 186 has the microcontroller select the clocking from the master clock signal through clock lines 47.

This step is performed after the master clock synthesizer 29 has stabilized in its new configuration.

The advantages of this device and method include, without limitation, very low production cost, very light weight, reduced need for inner shielding, very good performance 5 specifications in narrow resolutions, very good rejection of residual, spurious and image signals generated from the low-cost part selection, and accurate, repeatable measurements by connecting this device directly to the signal being measured without need for additional cables, similar to an RF power sensor but with full spectrum analysis and measuring receiver capabilities.

Those skilled in the art will recognize that numerous modifications and changes may be made to the preferred embodiment without departing from the scope of the claimed invention. It will, of course, be understood that modifications of the invention, in its various aspects, will be apparent to those skilled in the art, some being apparent only after study, others being matters of routine mechanical, chemical and electronic design. No single feature, function or property of the preferred embodiment is essential. Other embodiments are possible, their specific designs depending upon the particular application. As such, the scope of the invention should not be limited by the particular embodiments herein described but should be defined only by the appended claims and equivalents thereof.

I claim:

- 1. A spectrum analyzer system for measuring an RF signal over a selected frequency span comprising:

- a Radio Frequency/Intermediate Frequency (RF/IF) hardware section configured to convert the RF signal to a first IF signal using a first Local Oscillator (LO) signal with a first LO frequency;

- the RF/IF hardware section further configured to convert the RF signal to a second IF signal using a second LO signal with a second LO frequency different from the first LO frequency;

- the RF/IF hardware section further configured to select one of a primary IF path and a secondary IF path to filter the first IF signal, the primary IF path having a different pass 40 band center frequency than the secondary IF path and select one of the primary IF path and the secondary IF path to filter the second IF signal;

- the RF/IF hardware section further configured to convert the first IF signal to a first set of digitized IF signal 45 samples then convert the second IF signal to a second set of digitized IF signal samples;

- a processor configured to convert the first and second set of digitized IF signal samples to first and second sets of frequency domain samples;

- the processor further configured to combine the first and second set of frequency domain samples into a combined set of frequency domain samples; and a display configured to visually present the combined set of frequency domain samples.

- **2.** A Radio Frequency/Intermediate Frequency (RF/IF) hardware section for converting an RF signal over a selected frequency span comprising:

- a RF portion configured to sequentially convert the RF signal to a first IF signal using a first Local Oscillator 60 (LO) signal from a local oscillator, the first LO signal with a first LO frequency, then convert the RF signal to a second IF signal using a second LO signal from the local oscillator, the second LO signal with a second LO frequency different from the first LO frequency;

- an IF filtering portion configured to select one of a primary IF path and a secondary IF path to filter the first IF signal,

14

- the primary IF path having a different pass band center frequency than the secondary IF path, and configured to select one of the primary IF path and the secondary IF path to filter the second IF signal;

- an Analog to Digital Converter (ADC) configured to sequentially convert the first IF signal to a first set of digitized IF signal samples and then convert the second IF signal to a second set of digitized IF signal samples; and

- a data port configured to transmit the first and second set of digitized IF signal samples out of the RF/IF hardware section.

- 3. The Radio Frequency/Intermediate Frequency (RF/IF) hardware section of claim 2, wherein the RF/IF hardware section is further configured to sequentially convert the RF signal to the first set of digitized IF signal samples before converting the RF signal to the second set of digitized IF signal samples.

- **4.** A Radio Frequency/Intermediate Frequency (RF/IF) hardware section for converting an RF signal over a selected RF frequency span comprising:

- a master Voltage Controlled Oscillator configured for generating a master VCO signal with a master VCO frequency;

- an LO divider configured for generating an LO signal based on the master VCO signal by dividing the master VCO frequency by an LO divisor;

- a clock divider configured for generating a master clock signal based on the master VCO signal by dividing the master VCO frequency by a clock divisor different from the LO divisor;

- a mixer configured to convert the RF signal to an IF signal using the LO signal;

- an ADC further configured to convert the IF signal to a set of digitized IF signal samples using the master clock signal; and

- a microcontroller clocked by the master clock signal, wherein the microcontroller is further configured to change a frequency of the master clock signal by changing the clock divisor and changing a frequency of the LO signal from a first LO frequency to a second LO frequency by changing the LO divisor, if a center frequency of the selected RF frequency span after conversion to the IF signal is within half of a bandwidth of the ADC of a frequency of a spurious signal that occurs when using the first LO frequency.

- 5. A Radio Frequency/Intermediate Frequency (RF/IF) hardware section for measuring an RF signal over a selected frequency span comprising:

- an RF/IF convertor configured to convert the RF signal to a first IF signal using a first Local Oscillator (LO) signal with a first LO frequency, the RF/IF convertor further configured to convert the RF signal to a second IF signal using a second LO signal with a second LO frequency different from the first LO frequency;

- a wideband synthesizer configured for generating a local voltage controlled oscillator signal with a local voltage controlled oscillator frequency equal to a reference signal frequency times a counter factor, where the counter factor is equal to an integer A, plus a numerator B divided by denominator C, the quantity divided by 2 to a power of a post-scalar factor P, where numerator B is a number less than 900, where post-scalar factor P is a number with a value in a range of 0 to 10 inclusive, where C is a prime number equal or greater than 2 and less than 900;

- the wideband synthesizer further configured for generating the first LO signal based on the local voltage controlled oscillator signal by dividing the local voltage controlled oscillator frequency by a first denominator;

- a low band divider configured for generating the second 5 LO signal based on the first LO signal by dividing a first LO signal frequency of the first LO signal by a second denominator; and

- a microcontroller configured to provide the wideband synthesizer with, denominator C, first and second denominators.

- **6.** A method for measuring an RF signal over a selected RF frequency span comprising the steps of:

- generating, with master Voltage Controlled Oscillator (VCO), a master VCO signal with a master VCO frequency;

- generating, with a second stage LO, a second stage LO signal based on the master VCO signal by dividing the master VCO frequency by using a second stage LO divisor;

- generating, with the master VCO, a master clock signal based on the master VCO signal by dividing the master VCO frequency by a clock divisor different from the second stage LO divisor;

- converting, with a second stage mixer, a first stage IF signal 25 to a second stage IF signal using the second stage LO signal;

- converting the second stage IF signal to a set of digitized IF signal samples using an ADC clocked by the master clock signal;

- clocking a microcontroller using the master clock signal; and

- changing, with the microcontroller, a frequency of the master clock signal by changing the clock divisor and changing a frequency of the second stage LO signal by changing the second stage LO divisor, if a center frequency of the selected RF frequency span after conversion to the second stage IF signal is within half of a bandwidth of the ADC of a known spurious signal.

- $7.\,\mathrm{A}$  method for a spectrum analyzer system to measure an  $^{40}$  RF signal over a selected RF frequency span, the method comprising the steps of:

- selecting a mixer for a first sampling from one of a high band mixer and a low band mixer;

- selecting an intermediate frequency (IF) for the first sampling from one of a primary IF and secondary IF;

- setting a set of RF/IF path switches to create a first signal path through the mixer selected for the first sampling and through an IF path associated with the IF selected for the first sampling;

- selecting a first local oscillator (LO) frequency;

- generating, with a first stage LO, a first stage LO signal at the first LO frequency;

- converting, with the mixer selected for the first sampling, the RF signal to a first IF signal using the first stage LO 55 signal at the first LO frequency;

- sampling the first IF signal to obtain a first set of digitized IF samples;

16

- selecting a mixer for a second sampling from one of the high band mixer and the low band mixer;

- selecting an intermediate frequency (IF) for the second sampling from one of the primary IF and the secondary IF:

- setting the set of RF/IF path switches to create a second signal path through the mixer selected for the second sampling and through an IF path associated with the IF selected for the second sampling;

- selecting a second LO frequency different from the first LO frequency;

- generating, with the first stage LO, the first stage LO signal at the second LO frequency;

- converting, with the mixer selected for the second sampling, the RF signal to a second IF signal using the first stage local oscillator LO signal at the second LO frequency;

- sampling the second IF signal to obtain a second set of digitized IF samples;

- transforming, with a processor, the first and second sets of digitized IF samples into a first and a second set of frequency domain samples; and

- combining the first and second set of frequency domain samples into a combined set of frequency domain samples.

- 8. The method of claim 7, wherein:

- selecting the first LO frequency is based on the selected span and the IF selected for the first sampling; and

- selecting the second LO frequency is based on the selected span and the IF selected for the second sampling.

- **9**. The method of claim **7**, further comprising the step of displaying the combined set of frequency domain samples.

- 10. The method of claim 7, further comprising the step of storing the combined set of frequency domain samples.

- 11. A method to eliminate spurious signals when taking an RF signal over a selected frequency span with a center frequency, converting the RF signal to an IF signal with an LO signal from an LO (Local Oscillator), then converting the IF signal to a digital IF signal with an ADC (Analog to Digital Convertor), the method comprising the steps of:

- providing, from a clock synthesizer, the LO signal to the LO, and a clock signal to the ADC;

- wherein the clock synthesizer has a clock configuration comprising parameters that determine the frequency of the LO signal and the clock signal;

- changing, with a microcontroller, the clock configuration to a first clock configuration;

- changing, with a microcontroller, the clock configuration to a second clock configuration if the center frequency of the selected span after conversion to an IF signal is within half of a bandwidth of the ADC of a first known spurious signal or integer multiples thereof; and

- changing, with a microcontroller, the clock configuration to a third clock configuration if the center frequency of the selected span after conversion to an IF signal is within half of a bandwidth of the ADC of a second known spurious signal or integer multiples thereof.

\* \* \* \* \*